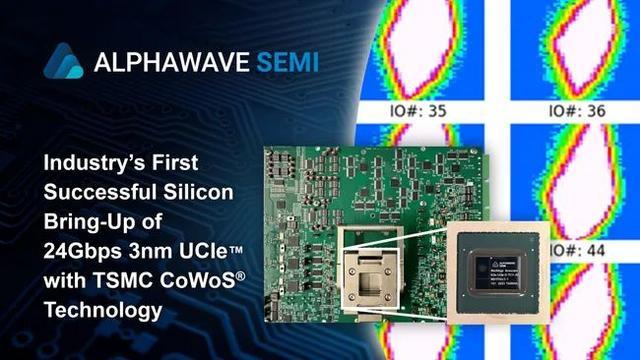

IT之家 8 月 1 日讯息,Alphawave Semi 公司最新研发出业界首款 3nm UCIe 芯粒(chiplet),为剿袭台积电 CoWoS 封装工夫的系统级封装(system-in-packages,SiP)竣事 die-to-die 结合。

该芯粒组面向超大鸿沟、高性能诡计和东说念主工智能等高需求领域,让用户构建多样系统级封装。

Alphawave Semi 高档副总裁兼定制硅和 IP 总司理 Mohit Gupta 暗示:

诈欺台积电的先进封装告捷推出 3 纳米 24 Gbps UCIe 子系统,是 Alphawave Semi 的一个要紧里程碑,在诈欺台积电 3DFabric 生态系统方面,彰显了公司顶级结合科罚有规划的专科智商。

该 3nm 芯粒固然也不错单独用于结合合适 UCIe 1.1 圭臬的芯粒,但该 IP 的主要用途是集成到其他芯粒中,让 Alphawave Semi(为其客户)或获取 IP 授权的公司竣事 die-to-die 结合。

历程硅考证的 3nm die-to-die 接口 IP 对商场敬爱紧要,它不错诈欺台积电迄今为止发轫进的制造工艺构建多芯粒 SiP。

该 3 纳米芯粒相沿 8 Tbps / mm 的带宽密度,剿袭台积电 CoWoS 2.5D 硅中介层(silicon-interposer-based)封装,包含物理层和限度器 IP,场外配资相沿 PCIe、CXL、AXI-4、AXI-S、CXS 和 CHI 等多种条约。

Alphawave Semi 的 UCIe 子系统 IP 合适最新的 UCIe 秩序 Rev 1.1,并配备了渊博的测试和调试功能,包括 JTAG、BIST、DFT 和 Known Good Die(KGD)功能。

IT之家简要先容下本文中波及的关联独到名词:

Die:裸晶,所以半导体材料制作而成、未经封装的一小块集成电路内容,该集成电路的既定功能便是在这一小片半导体上竣事。

Chiplet:芯粒是一个袖珍集成电路,包含明确界说的功能子集。它被遐想为与单个封装内插器上的其他小芯片结合在沿途。一组芯粒不错在混杂搭配“乐高式”堆叠组件中竣事。

UCIe:全称为 Universal Chiplet Interconnect Express,译为通用芯粒互连,是一种通达规格,适用于芯粒之间的裸晶互连与序列总线。

CoWoS:不错分红“CoW”和“WoS”来看:“CoW(Chip-on-Wafer)”是芯片堆叠;“WoS(Wafer-on-Substrate)”则是将芯片堆叠在基板上。

系统级封装:一种集成电路封装的看法,是将一个系统或子系统的全部或大部分电子功能建树在集成型衬底内,而芯片以 2D、3D 的神气接合到集成型衬底的封装神气。